Overview

Explore a 20-minute conference talk presented at the 2018 IEEE Symposium on Security & Privacy, focusing on vRAM, a novel system for verifiable computation of RAM programs. Delve into the innovative approach that introduces circuit-independent preprocessing, allowing for efficient verification of arbitrary RAM programs without sacrificing expressiveness. Discover how vRAM achieves asymptotically optimal prover overhead and significantly reduces memory consumption and running time compared to existing schemes. Learn about the system's ability to scale to RAM computations with over 2 million CPU cycles, representing a substantial improvement in the field. Examine the experimental results demonstrating vRAM's performance advantages and its potential impact on delegating computations securely and efficiently.

Syllabus

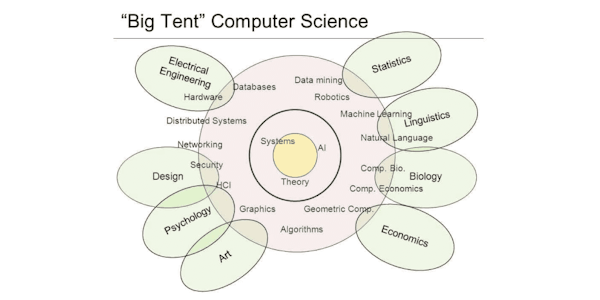

Intro

Delegating Computations

Verifiable Computation (VC)

Efficiency Measures of Verifiable Computation

Prior Work in Verifiable RAM

Our Construction: VRAM

Verifiable RAM Constructions

Front-end

Tradeoff of Existing Work

Improvements on the Backend

Experimental Results

Taught by

IEEE Symposium on Security and Privacy