Stanford Seminar - Dataflow for Convergence of AI and HPC - GroqChip

Stanford University via YouTube

Overview

Syllabus

Introduction

Dennis Axe

Hardware Software Interface

Pipeline

Core Architecture

Superlane Architecture

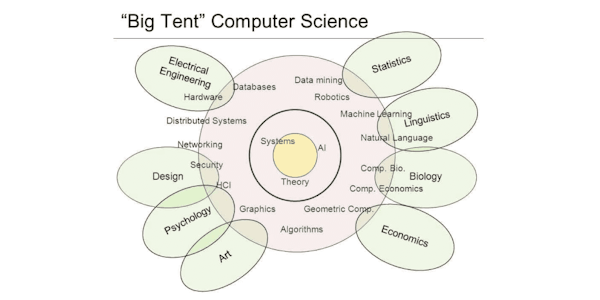

DomainSpecific Architecture

Data Types

Communication and Computation

Energy Difference

Functional Control Units

Superlane

Vector Processor

Memory System

Switch Execution Module

System Architecture

Topology

Packaging

Network

Normal RDMA

Communication model

Synchronous communication

Taught by

Stanford Online