Overview

Syllabus

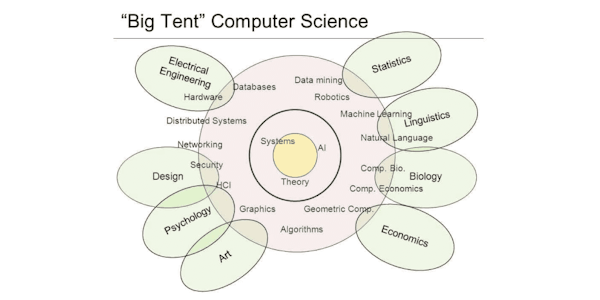

Introduction.

Technology in banking - a problem in scale and complexity.

Fastest computers for top 4 HPC applications.

Commercializing FPGAs for Computation.

Conflicts We live in a world of many conflicts.

New Conflicts.

The Kill Switch Product Idea.

Uncertainty.

The Homework Problem.

Start a company, build a product Pain Points.

Scaling is a race against cashflow.

Top 10 Conflicts in Computing with FPGAS Conflict 1: HDL is hard, need a high level programming language Conflict 2: FPGAS DRAM Memory interfaces.

HDL is hard, high level programming.

C1: Connect language to space on the chip.

FPGA floating point is inefficient (due to the barrel shifter).

Separating CPUs and FPGAS Conflict: CPU and FPGA in the same server is inefficient. The optimal balance between FPGAs and CPUs is never exactly 50-50, Server+FPGA card is inefficient Solution: build an Infiniband-connected appliance.

There are no Applications for FPGAS Why would you buy a computer for which there are no applications.

Need to rewrite parts of the application Solution 1: Develop the Maxeler acceleration process.

Hardware Debug is Hard MaxDebug tool example.

C7 Hardware Efficiency Debug is Hard.

c7 Hardware Performance Debug is Hard MaxProfile tool example.

Place-and-route takes 3 days.

High level language obsoletes the HDL expert.

Most software does not need acceleration.

Conclusions To scale, you need to keep up with the conflict cycle, predict and solve the next next conflict before it happens!.

World's hardest simulation, Quantum Chromodynamics on a Xilinx VU9P FPGA.

Taught by

Stanford Online